Research Update Pg 28

**Signal Integrity:** In-between spaces Pg 30

Analog Domain: Confer for continuing education Pg 32

**Issue 11**/2007

www.edn.com

Tales from the Cube: The power of the hot seat Pg 34

**Design Ideas** Pg 103

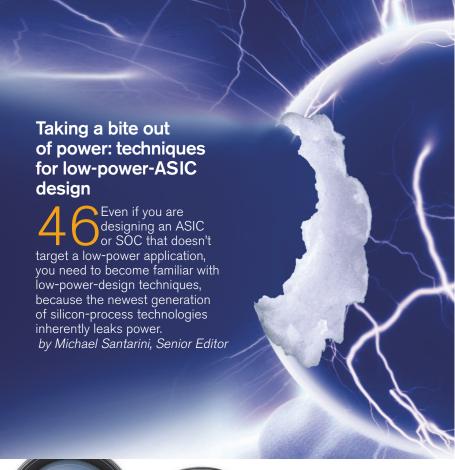

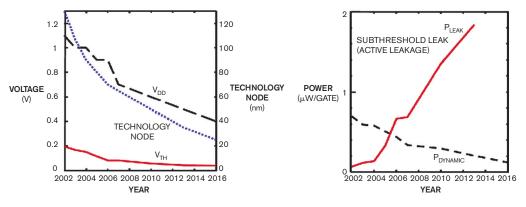

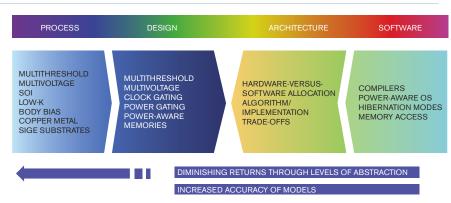

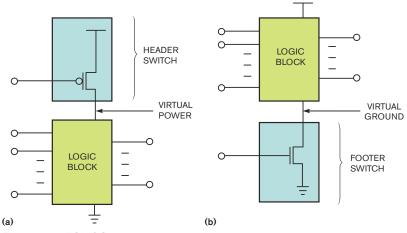

# TAKING A BITE OUT OF POWER: TECHNIQUES FOR LOW-POWER-ASIC DESIGN

Page 46

RENEW

your FREE **magazine** subscription

START

a FREE **e-newsletter** subscription

COMPACTIMAGING SYSTEMS

FACE PARTITIONING ISSUES

Page 37

ESTIMATING THE ZIGBEE TRANSMISSION-RANGE ISM BAND

Page 67

DESIGNING MEDICAL DEVICES

FOR ISOLATION AND SAFETY

Page 75

REDUCING POWER CONSUMPTION IN BATTERY POWERED APPLICATIONS

Page 81

SMIALL, HIGH-PERFORMANCE ICS REQUIRE WAFER-LEVELRE MEASUREMENTS

Page 91

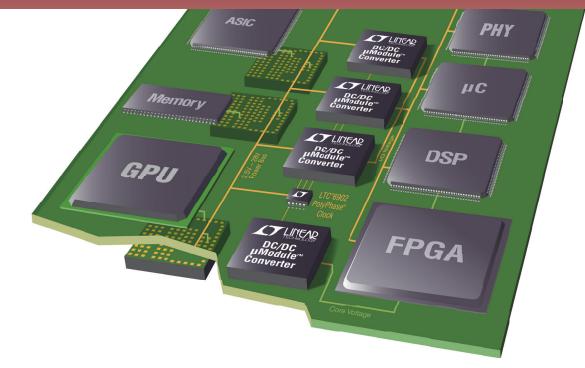

# Digital Power for a Changing World

Adaptable, High-Density, Multi-functional POL Controller

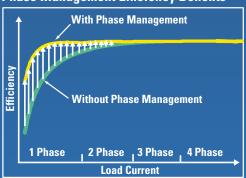

The new UCD9240 Fusion Digital Power™ point-of-load (POL) controller from Texas Instruments gives designers faster time to market without sacrificing features or performance. This flexible and adaptable multi-rail controller provides high power density, dynamic power supply, load-optimized phase management and configurable sequencing.

#### **Phase Management Efficiency Benefits**

High-Performance Analog >> Your Way

For evaluation modules and data sheets, visit >> www.ti.com/digitalpower 1-800-477-8924 ext 9240

High-Performance Analog >> Your Way, Fusion Digital Power, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1823A0 © 2007

Access to more than a million products now available online!\*

Same-day shipment, next-day delivery on orders entered by 8:00 PM CST.

Quality Electronic Components, Superior Service

www.digikey.com

1.800.344.4539

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

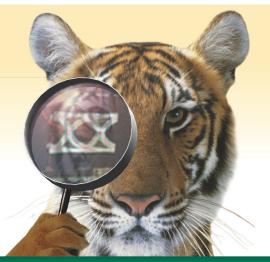

## **Ancient Methods of Protection Will Only Take You So Far.**

When it comes to thwarting 21st century evildoers, nobody has more industry-proven secure IC solutions than Atmel®.

With a broad portfolio of biometric sensors, embedded security chips, RF identification chips, secure microcontrollers and secure memories for smart cards, and RFID/card readers, Atmel has the expertise and flexibility to provide customer-driven solutions for security in an unsecured world.

And, when it comes to measuring why we're good, don't just take our word for it. Our secure microcontroller product portfolio meets the stringent needs of the security market with some of the highest security certifications in the industry, including Common Criteria EAL4+/EAL5+, FIPS-140-2 Level 3 and 4, ZKA, Visa® International and MasterCard CAST approvals.

So, when your next project calls for security, think Atmel. We're Everywhere You Are®... securely.

Secure Memory and Microcontrollers for Smart Cards

Smart Card Reader ICs

Biometrics

Trusted Platform Module IC

**Embedded Security**

RF Identification

Check out Atmel's security solutions today at www.atmel.com/ad/securitysolutions

# **Comprehensive Analog Portfolio**

High-Performance Analog >> Your Way™

#### **AMPLIFIERS**

**Audio Amps Buffer Amps Difference Amps High-Speed Amps Instrumentation Amps Isolation Amps** Log Amps **Low-Voltage Op Amps Power Op Amps Precision Op Amps Programmable Gain Amps Video Amps**

ADS5546

TPS40140

IS0721

### DATA CONVERTERS

**Audio ADCs Delta-Sigma ADCs Pipeline ADCs SAR ADCs Audio DACs Current-Steering DACs Delta-Sigma DACs Precision DACs General-Purpose DACs Audio SRCs Data Acquisition Systems** Modulators/Filters

#### POWER MANAGEMENT

**Battery Management Charge Pumps** DC/DC Switching Controllers **DC/DC Switching Converters Digital Power Display Drivers Hot Swap LED Drivers Linear Regulators MOSFET Drivers** Plug-In Modules **Power Factor Correction Power Supply Control**

#### INTERFACE

1394 CAN **Circuit Protection Digital Isolators Display Interface** LVDS/MLVDS PCIe/PCI RS-485, 232 & 222 SCSI **Serializers Deserializers Transceivers UARTs** USB

4-20 mA Transmitters **Analog ASSPs Analog MUXs Clocks & Timers Comparators Current Shunt Monitors Digital Up Converters Digital Down Converters Fan Controllers ISM Band** References **Switches Temp Sensors** ZigBee™

**HIGH-PERFORMANCE ANALOG**

YOUR WAY

Texas Instruments offers a comprehensive high-performance analog portfolio from amplifiers and data converters to power management and interface. Whether you need faster speed, higher precision, lower power or smaller size, TI has analog ICs to differentiate your design. That's High-Performance Analog >> Your Way.

**OPA211 Low-noise, low-power, 36V bipolar op amp** (1nV/\daggedHz; 3.5mA) in small MSOP-8 package **OPA333**

**Lowest power, zero-drift op amp:** 2µA offset, 17µA current, SC70 and SOT23 packages

ADS8422 Fastest 16-bit SAR ADC (4MSPS) 2LSB INL, 92.5dB SNR

Fastest 14-bit ADC (190MSPS) 73.2 SNR at 70MHz IF; 84dBc SFDR at 70MHz IF; 1.1W power

High-speed digital isolator: 4000V (peak) isolation; signaling rate of 0-150Mbps; high electromagnetic immunity; low input current requirement; failsafe output

TAS5261 PurePath Digital™amplifier capable of driving more than 300W

96% efficient buck-boost converter with up to 28% greater run-time; 3 x 3 mm<sup>2</sup> QFN package TPS63000

> Stackable, scalable, flexible PWM buck controller generates 10A to 320A of output current and enables maximum efficiency up to 16 phases

All other trademarks are the property of their respective owners. 1789A0 © 2007 To

www.ti.com/analog

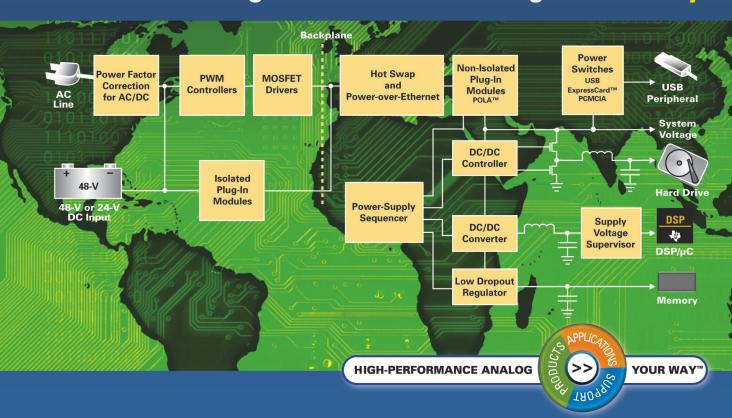

# **Power From AC Line to POL**

**High-Performance Analog** >> **Your Way**

TI's broad portfolio of line power solutions includes AC/DC and DC/DC conversion, digital power, hot swap, MOSFET drivers, PoE controllers, plug-in modules and power switches. With design software, reference designs, on-line training, local support and more, TI has the tools you need to meet your design challenges. That's High-Performance Analog>>Your Way.

| UCC28600                | 8-pin offline quasi-resonant converter offers exceptional efficiency at high and standby power levels            |

|-------------------------|------------------------------------------------------------------------------------------------------------------|

| UCC27200                | 120-V high-side, low-side MOSFET 3-A driver improves efficiency of half-bridge topologies                        |

| TPS40140                | 1 stackable 2-channel multiphase or 2-channel independent output DC/DC controller                                |

| TPS5430                 | Easy-to-use 5.5-V to 36-V input, 500-kHz, 3-A SWIFT™ DC/DC converter                                             |

| TPS2410/1/<br>TPS2412/3 | ORing-diode FET controllers reduce power loss and protect server and telecom power systems from transient events |

| PTH08T230W              | 6-A, 4.5-V to 14-V input, non-isolated, wide output-adjustable power module with<br>TurboTrans™Technology        |

| PTQB425080              | 200-W, 48-V input, 8-V output, isolated DC/DC bus converter                                                      |

| DCH0105                 | Miniature 1-W, 3-kVDC isolated DC/DC converter                                                                   |

NEW Power Management Selection Guide, design software and reference designs >>>

www.ti.com/linepower 1.800.477.8924 ext.1104

High-Performance Analog >> Your Way, Technology for Innovators, SWIFT, TurboTrans and the red/black banner are trademarks of Texas Instruments, All other trademarks are property of their respective owners, 1821A0 @ 2007 TI

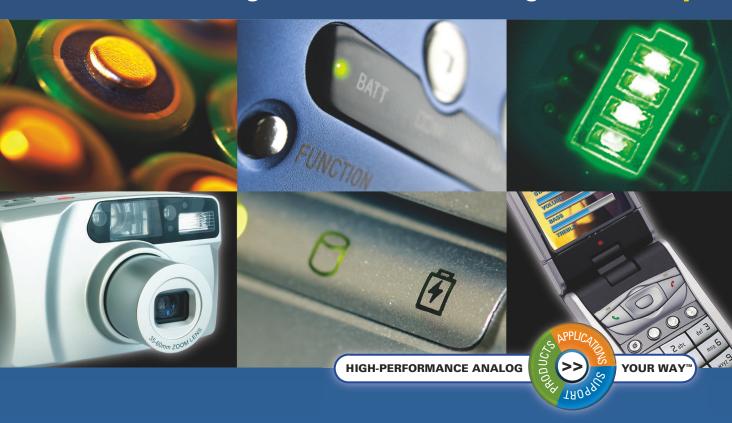

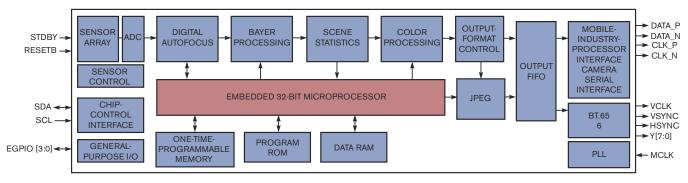

# **Portable Power Management**

**High-Performance Analog** >> Your Way

TI delivers high-performance and integrated power management solutions to fit battery power design challenges for a variety of applications, including cell phones, digital cameras, notebook computers and more. Tl's applications knowledge and unique manufacturing capabilities, combined with local technical support, allow us to deliver innovative power management products for the most demanding portable power designs. That's High-Performance Analog >> Your Way.

TPS63000

TPS799xx

TPS62110

TPS62350

TPS61081

bq24060

bq20z90

TPS65050

TPS65050

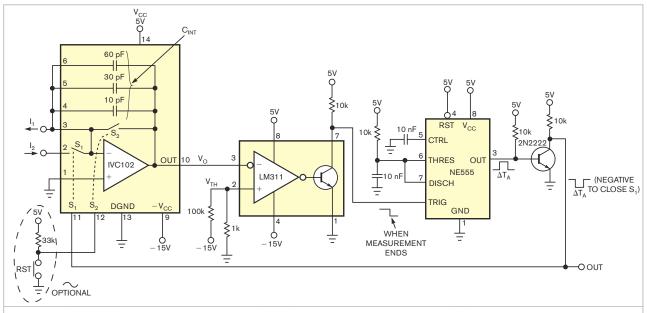

96% efficient, buck/boost DC/DC converter: 1.2-A, in 3 x 3 mm² QFN

Low-noise, low dropout regulator: 200-mA, 40-μA I<sub>Q</sub>, high PSRR, in WCSP

1.5-A step-down DC/DC converter: synchronous, 17-V<sub>IN</sub>, up to 95% efficiency

800-mA step-down converter with I²C: 3-MHz, 2.7-V to 6-V<sub>IN</sub>, in WCSP

High-voltage boost converter: 27-V<sub>QUT</sub>, integrated 1.3-A switch

Linear 1-cell, Li-lon battery charger: thermal regulation, 6.5-V OVP, temp sense

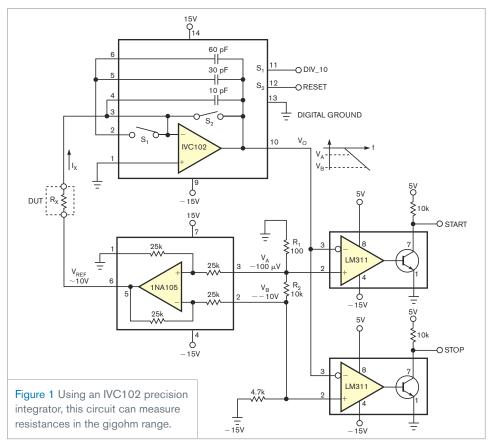

Li-lon battery gas gauge: 99% accuracy, Impedance Track™ Technology, SBS 1.1-compliant

6-channel PMU: 2 DC/DCs and 4 LDOs, 4 x 4 mm² QFN, up to 95% efficiency

6-channel PMU with I²C: 3 DC/DCs and 3 LDOs, DVS, in 5 x 5 mm² QFN

Get samples, evaluation modules and access the online Power Management search tool at >> www.ti.com/portable 1.800.477.8924 ext.1103

Impedance Track, High-Performance Analog >> Your Way, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1805A0 © 2007

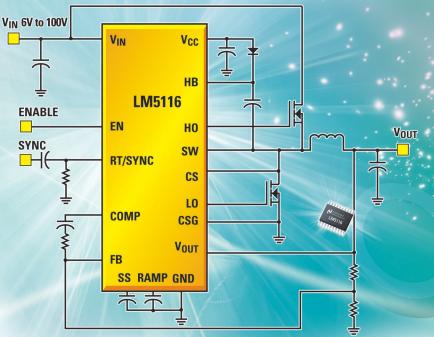

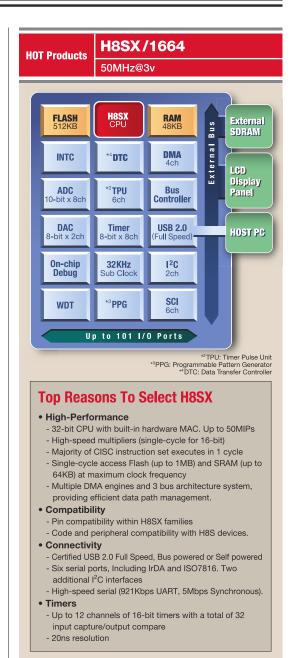

# Industry's First 6V to 100V Current-Mode Buck Controller

LM5116 Synchronous Controller Features Emulated Current Mode (ECM) Control for High Step-Down Ratio

#### **LM5116 Features**

- Ultra-wide input range: 6V to 100V

- Programmable output from 1.215V to 80V

- Less than 10  $\mu$ A  $I_q$  in sleep mode

- Frequency adjustable to 1 MHz with sync capability

- Programmable soft-start

- Drives standard or logic-level MOSFETs

- RDS(ON) or resistor current sensing

- · Controlled start-up into pre-biased load

- Available in thermally enhanced TSSOP-20 packaging

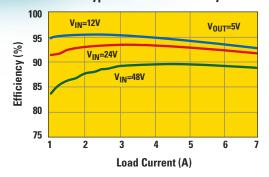

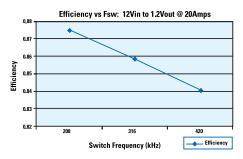

#### **Typical Circuit Efficiency**

Ideal for use in telecommunications, automotive, and industrial control applications

For FREE samples, datasheets, and more information on the LM5116, contact us today at: power.national.com

Or call: 1-800-272-9959

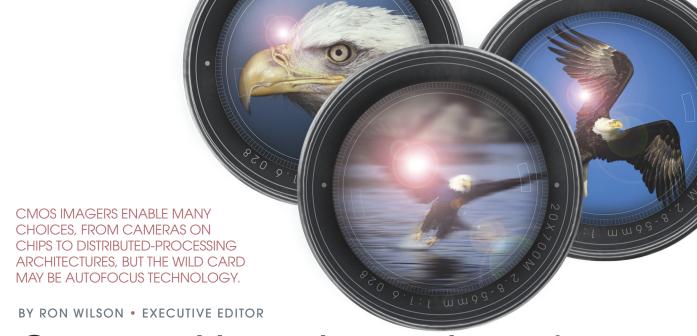

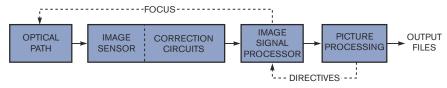

#### Compact imaging systems face partitioning issues

CMOS imagers enable many choices, from cameras on chips to distributed-processing architectures, but the wild card may be autofocus technology.

by Ron Wilson, Executive Editor

#### **Estimating the ZigBee** transmission-range ISM band

Designers of shortrange wireless devices in the 900-MHz and 2.4-GHz band need to understand what and how parameters affect the transmission range based on formulas and be able to apply them in formulas for statistically calculating the path loss and range for both indoor and outdoor environments. by Shreharsha Rao, Texas Instruments

# EDN contents 5,24,07

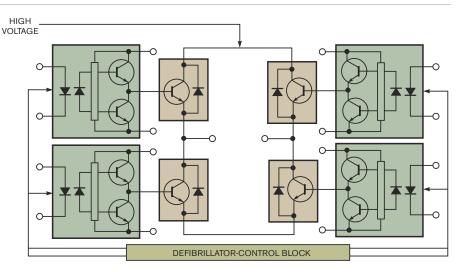

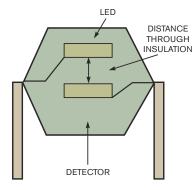

#### **Designing medical** devices for isolation and safety

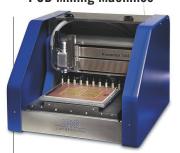

Optocouplers and sound design practices provide effective isolation for medical equipment and protect patients from leakage currents. by Yeo Siok Been, Jamshed Namdar Khan, and Derek Chng Peng Hui, Avago Technologies

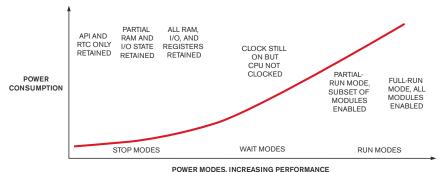

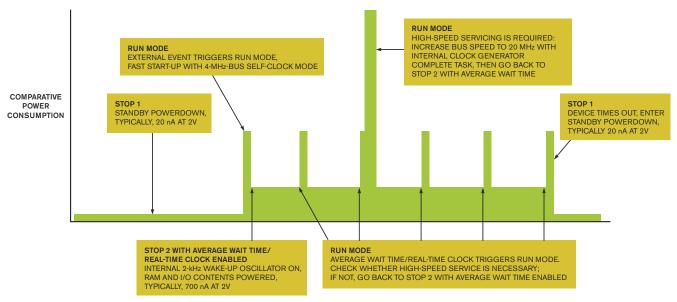

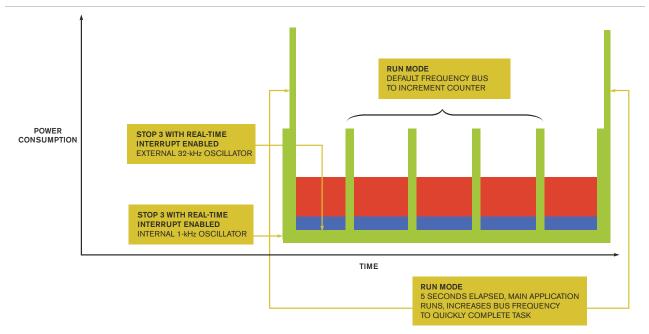

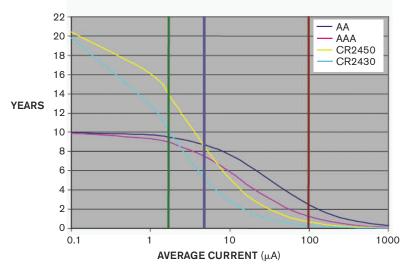

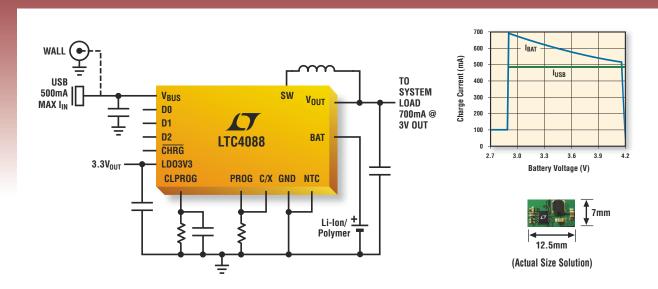

#### Reducing power consumption in batterypowered applications

Using the lower power modes of advanced microcontrollers means less battery drain in parked automobiles and longer battery life in portable consumer products.

by Matt Ruff. Freescale Semiconductor

#### Small, high-performance ICs require waferlevel-RF measurements

Although accurate and repeatable results require different instrumentation and techniques, don't be intimidated by wafer-level-RF measurements. by Larry Dangremond,

Cascade Microtech

### ESIGNIDEAS

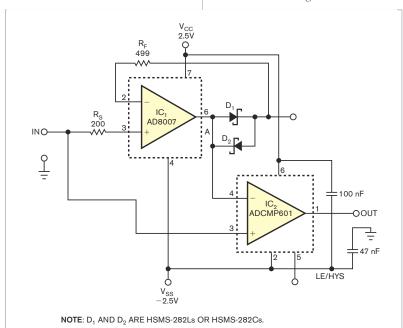

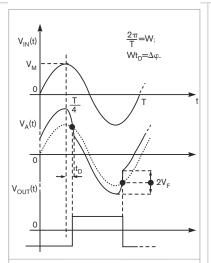

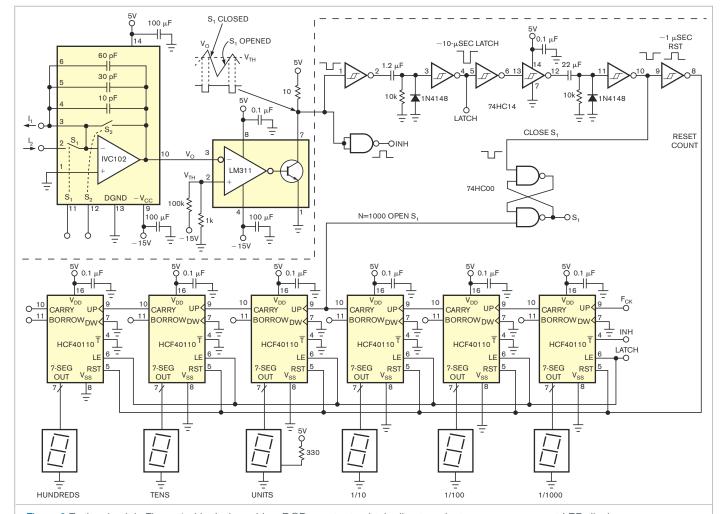

- 103 Comparator detects position of peaks and valleys in a waveform

- 104 Precision integrator sparks current-ratio-to-frequency converter

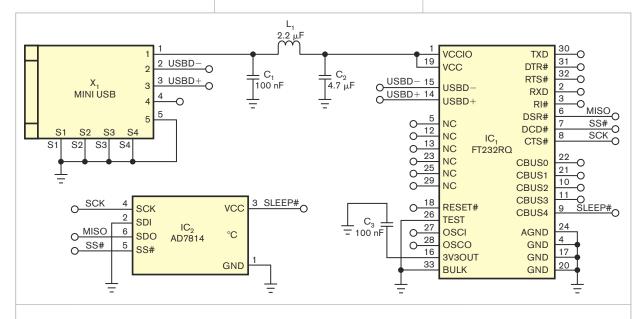

- 108 Accurate USB 2.0 temperature sensor needs only a handful of parts

- 110 Integrator enables simple ohmmeter with gigohm range

# M-LVDS - The Bus Standard

#### **Signal Integrity for Backplanes and Cables**

#### **Applications**

- AdvancedTCA (ACTA) and MicroTCA

- Clock, data, sync and control

- Cellular base stations

- Central-office switches

- Test and measurement

#### **Features**

- Meets M-LVDS (TIA/EIA-899)

- 11.3mA driver output current

- 50mV receiver thresholds

- Contention provisions:

- Driver short-circuit limited to 43mA

- Devices limit bus voltage from 0 to 2.4V

- Drivers tested with 32 contending nodes

- Failsafe support

HIGH-PERFORMANCE ANALOG

Texas Instruments provides a broad range of innovative Multipoint LVDS (M-LVDS) devices that deliver the speed, power and robustness required for backplane and multipoint bus applications. With contention features for data and control signals, single- and eight-channel transceivers, a quad driver, single-channel receivers, and clock buffer devices for 1:8 and dual 1:4 fan-outs, TI's M-LVDS products are ideal for distributing clock and synchronization signals.

| Device       | Signaling<br>Rate (Mbps) | No. of<br>Tx / Rx | Input         | Output        | ESD HBM<br>(kV) | Function                                 |

|--------------|--------------------------|-------------------|---------------|---------------|-----------------|------------------------------------------|

| SN65MLVD047A | 200                      | 4/0               | LVTTL         | M-LVDS        | 9               | Quad Driver                              |

| SN65MLVD080  | 250                      | 8/8               | LVTTL, M-LVDS | M-LVDS, LVTTL | 8               | Octal Half-Duplex Transceiver            |

| SN65MLVD128  | 250                      | 8/1               | LVTTL         | M-LVDS        | 9               | Repeater                                 |

| SN65MLVD201  | 200                      | 1/1               | LVTTL, M-LVDS | M-LVDS, LVTTL | 8               | Half-Duplex M-LVDS Transceiver           |

| SN65MLVD207  | 200                      | 1/1               | LVTTL, M-LVDS | M-LVDS, LVTTL | 8               | Full-Duplex M-LVDS Transceiver           |

| SN65MLVD2    | 250                      | 0/1               | M-LVDS        | LVTTL         | 8               | Single Channel M-LVDS Receiver           |

| SN65MLVD3    | 250                      | 0/1               | M-LVDS        | LVTTL         | 8               | Single Channel M-LVDS Type-2<br>Receiver |

New products listed in red

For evaluation modules, data sheets and samples visit >> www.ti.com/mlvds 800. 477. 8924 ext.13841

High-Performance Analog >> Your Way, Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1853A0 © 2007 TI

#### contents 5.24.07

- Blade computer sports four cores

- Synchronizable POL converters beat the noise

- 22 100M-sample/sec, 14-bit digitizer and 25- and 50-MHz digital-I/O modules are first to support PXIe

- 22 AC/DC supply achieves 11.2W/in.3

28 Research Update: Nanocomposites promise advance in thin-film electronic components;

26 Atmel's AVR32 UC3 processor boasts low power

NEC plastic cools the palm and the earth; Energy harvester generates continuous nanoampere

current

#### **DEPARTMENTS** & COLUMNS

- 14 EDN.comment: Unique IP addresses will prove main IPv6 benefit

- 30 **Signal Integrity:** In-between spaces

- 32 **Analog Domain:** Confer for continuing education

- 34 Tales from the Cube: The power of the hot seat

- 124 **Scope:** Electronic Materials Conference. biopotential sensors, and a consumer-driven electronics industry

# PRODUCT

- 117 **Power Sources:** Quarter-brick, dc/dc-power modules; photovoltaic and wind converters; eighthand quarter-brick intermediate-bus architectures; and more

- 119 **Microprocessors:** 16-bit-microcontroller family, decoders for HD-DVD and Blu-ray-disc players, configurable SOCs, embedded USB controllers, and more

- 121 Embedded Systems: DVI controllers, wireless embedded-networking modules, GPS receivers, and more

EDN® (ISSN#0012-7515), (GST#123397457) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2007 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: U.\$, \$165 one year, Canada, \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elseviei Properties Inc. used under license, A Reed Business Information Publication/Volume 52, Number 11 (Printed in USA).

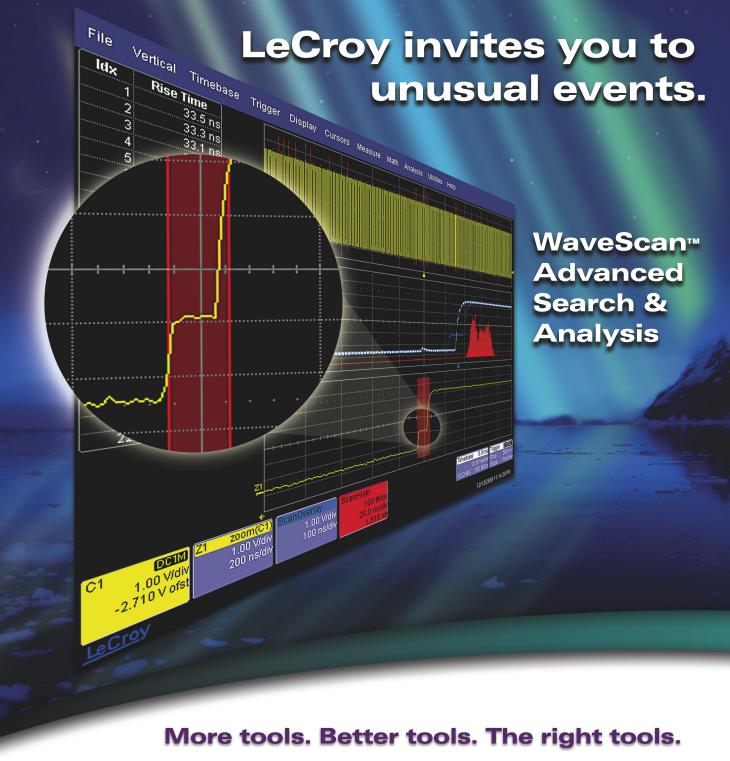

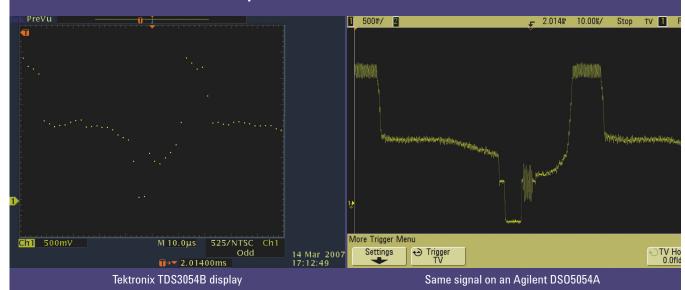

WaveScan, a powerful new tool only for LeCroy oscilloscopes, continuously monitors live acquisitions for unusual events – even if you're not there.

Select from more than 20 search criteria, including frequency, rise time, runt, and duty cycle. WaveScan also locates rare occurrences in a single capture, or even a saved waveform and marks events for quick identification. Debug faster. It's that simple.

EDN Magazine has included LeCroy's WaveRunner® Xi and WaveSurfer® Xs with WaveScan in it's 'Hot 100 Products' list. WaveScan is also an EDN 2007 Innovation Award Finalist.

# EDN online contents

#### ONLINE ONLY

Check out these Web-exclusive items:

#### IBM air-gap dielectric literally full of holes

www.edn.com/070524toc2

#### Blend of optics, hardware, and software brings cell-phone cameras into focus

www.edn.com/article/CA6438794

#### Power-line promoters: Lawsuit candidates?

www.edn.com/070524toc4

#### Panelists discuss challenges of interoperable pcell effort

www.edn.com/article/CA6438809

#### Not your average power analyzer, dc unit makes short work of tedious test setups

www.edn.com/article/CA6433721

#### Micro Magic offers GDSII viewer tool for free (until DAC 2008)

www.edn.com/070524toc1

#### Cool or what? A solar-powered transistor radio from 1957

www.edn.com/070524toc3

#### **EDA start-up GateRocket brings** hardware-based accelerator to FPGA designers

www.edn.com/article/CA6435696

#### IC Manage announces new version of design-management software

www.edn.com/article/CA6435732

#### READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

#### Measuring nanoamperes

> www.edn.com/article/CA6434367

#### IBM details 3-D chip-stacking breakthrough

www.edn.com/article/CA6433308

#### Special Report: Inside the new multicore processors

www.edn.com/article/CA6434384

#### Hot, cold, and broken: Thermal-design techniques

> www.edn.com/article/CA6426879

#### Fooled by a thermocouple: Temperature sensing gone awry

www.edn.com/article/CA6430354

#### PCB road-kill

www.edn.com/070426t1

#### Choose capacitor types to optimize PC sound quality

www.edn.com/article/CA6430345

#### Wringing out thermistor nonlinearities

www.edn.com/article/CA6430356

#### TSMC talks details on the meaning of 45-nm CMOS

> www.edn.com/article/CA6434612

#### Lusting after 100% energy efficiency? Photosynthesis' quantum secret may hold key

www.edn.com/070524toc5

#### PRYING EYES COMES ALIVE

EDN's Prying Eyes articles, in which we tear into a product to reveal the engineering behind it, have proved popular. So we're now giving you the chance to explore some Prying Eyes projects in a multimedia Flash presentation. Check out:

#### Hybrids mark the end of the stinky city bus

www.edn.com/article/CA6437959

#### Exploring the foundation under smartphones

www.edn.com/article/CA6430344

#### Rummage through a Roomba

www.edn.com/article/CA6421379

#### A HEX (CODE) UPON US

In "Find hex-code values for microcontroller's ADC voltages" (April 12, 2007, www.edn.com/article/CA6430339), we flubbed a key formula. The typo made the Design Idea seem less impressive than it actually is and prompted some colorful reader comments. We have now corrected the online version, and the author has provided a look-up table, a handy Excel spreadsheet that allows you to interact with the formula, and some comments of his own.

#### SOME SHORTCUTS

#### Current issue and archives

www.edn.com/archive

#### Design Ideas

www.edn.com/designideas

#### Columnists

www.edn.com/columnists

#### Blogs

www.edn.com/blogs

#### **DSP Directory**

www.edn.com/dspdirectory

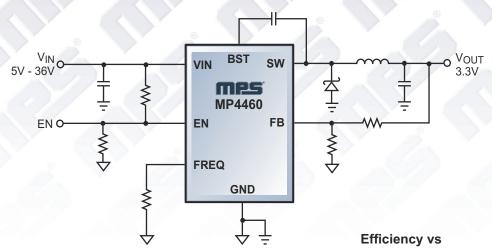

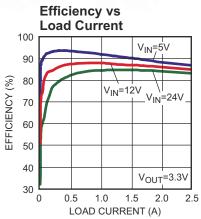

# 40V, 2.5A

### Non-Synchronous Buck Regulator

#### Ultra Compact, Simplified Design Solutions

- Adjustable Frequency Up to 4MHz

- ▲ Input Range 4.5V 40V (Max)

- 150mΩ Integrated Switch

- Compact QFN10 (3mm x 3mm) Package

- Only 10 External Components!

|        | Featured (High-Voltage) Non-Synchronous Bucks |                     |          |          |                    |  |  |

|--------|-----------------------------------------------|---------------------|----------|----------|--------------------|--|--|

| Part   | Frequency                                     | V <sub>IN</sub> (V) | VOUT (V) | IOUT (A) | Package            |  |  |

| MP4459 | 4MHz (Adj.)                                   | 4.5 - 40 (Max)      | 0.8 - 36 | 1.5      | TQFN10 (3mm x 3mm) |  |  |

| MP4460 | 4MHz (Adj.)                                   | 4.5 - 40 (Max)      | 0.8 - 36 | 2.5      | QFN10 (3mm x 3mm)  |  |  |

| MP2467 | 500KHz (Fixed)                                | 6 - 40 (Max)        | 0.8 - 30 | 2.5      | SOIC8E             |  |  |

| MP4461 | 4MHz (Adj.)                                   | 4.5 - 40 (Max)      | 0.8 - 36 | 3.5      | QFN10 (3mm x 3mm)  |  |  |

DC to DC Converters CCFL / LED Drivers Class D Audio Amplifiers Linear ICs

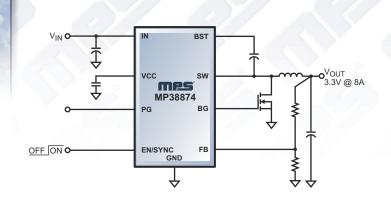

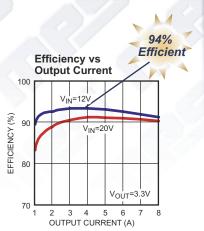

# 21V, 8A, 600KHz

#### Synchronous Buck Regulator

#### 45mΩ Internal Power MOSFET Switch

#### Only 8 External Components!

Actual Double Sided Footprint Solution Size

- Up to 8A for Today's High Performance Digital Core

- Stable with Low ESR Output Ceramic Capacitors

- Internally Compensated

- Integrated Soft Start

|         | Featured (High-Current) Synchronous Bucks |                     |                      |                      |             |  |  |  |

|---------|-------------------------------------------|---------------------|----------------------|----------------------|-------------|--|--|--|

| Part    | Frequency                                 | V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | I <sub>OUT</sub> (A) | Package     |  |  |  |

| MP38872 | 600KHz                                    | 4.5 - 21            | 0.8 - 15             | 6                    |             |  |  |  |

| MP38891 | 400KHz                                    | 4.5 - 30            | 0.8 - 15             | 6                    | QFN 14      |  |  |  |

| MP38874 | 600KHz                                    | 4.5 - 21            | 0.8 - 15             | 8                    | (3mm x 4mm) |  |  |  |

DC to DC Converters CCFL / LED Drivers Class D Audio Amplifiers Linear ICs

#### BY MAURY WRIGHT, EDITORIAL DIRECTOR

# Unique IP addresses will prove main IPv6 benefit

tarting in late 1999, I was editor of CommVerge, a short-lived sister publication to EDN that focused on the convergence trend. We launched just as the Internet went mainstream and folded with the so-called dot-com bust. In the first issue, my article "Maxed out" described the critical need for a move from IPv4 (Internet Protocol Version 4) to IPv6 (Internet Protocol Version 6) as the foundation of the

the burgeoning Internet (www.edn. com/article/CA41781). My primary thesis centered on the shortage of unique IP addresses that 32-bit IPv4 afforded. Now, a number of measures, such as NAT (network-address translation), seemingly have solved the address issues—or have they? Many good reasons still exist for devices to have globally unique IP addresses.

Acquaintances that use technology but aren't in the tech industry have been asking me about the concept of a new Internet to replace what we have. I think it's highly unlikely that we can develop an entirely new network and one day throw the switch to move from old to new, although I can see the clean-sheet-of-paper benefits when things such as security are concerned. I believe that it's more likely that we will continue to evolve the Internet and that a move to IPv6 almost a decade after I first thought it was a critical need would be a step in the right direction.

For a good update on the status of IPv6, you might check out a comprehensive package of stories that *eWeek* produced on the subject. The main story, "IPv6: Ready or not," and numerous sidebars describe the advantages

#### It's highly unlikely that we can develop an entirely new network and one day throw the switch to move from old to new.

of IPv6 and the obstacles to broad deployment (www.eweek.com/article2/0,1895,2126069,00.asp). The main eWeek article used the Katrina hurricane disaster to point out how IPv6 could have greatly improved quick deployment of a network after such a disaster. Quicker and simpler deployment would have accelerated recovery efforts. IPv6 would have simplified deployment because every IP-enabled device, including notebooks and even cell phones, could act as a server on the network, providing an immediate means to dynamically build a network.

I'd argue that IPv6 is also great in the embedded-device market in which more machines, sensors, and other noncomputer devices are network-enabled. Indeed, I'd encourage all engineers to design for IPv6 support even if they don't think that support is currently necessary. I'm hoping that IPv6 has simply been another victim of Leibson's Law (www.edn.com/blog/980000298/post/750007875. html). Steve Leibson, a Tensilica executive, EDN contributor and blogger, and former EDN editor in chief, observed that it takes any good idea a decade to matriculate and succeed. IPv6 was stable and ready for prime time around 1999. We should see a broad migration to IPv6 in the next few years.

Alas, I always expect technology change to happen more rapidly. Clearly, I was early in calling for IPv6 adoption at the beginning of 2000. At the time, it seemed necessary. I remember companies such as 3Com and Cisco having hordes of IP-address space and giving every employee a unique IP address, although, in their labs, they were working on NAT and similar technologies. Who knew that every wired home would have a NAT-enabled router and that broadband providers would dynamically assign IP addresses? I guess I can take solace in not being the only person alarmed by the disappearing address space.

I could have also used a dose of Leibson's Law before I wrote the editorial for that first issue of CommVerge. In "POTS: R.I.P.," I predicted the demise of analog telephones and a massive switch to VOIP (voice over IP) within a year or two (www.edn.com/article/CA41788). Well, I still have a POTS (plain-old-telephone-system) phone today. But here we are, more than seven years later, and VOIP is rapidly usurping POTS, and, by the time the clock strikes a decade, POTS will likely be gone. EDN

Contact me at mgwright@edn.com.

#### **MORE** AT EDN.COM

$\triangleright$

+ Go to www.edn.com/070524ed and click on Feedback Loop to post a comment on this column.

# Everything you need to save our world, 1mW at a time.

#### The Power Franchise®

Developing more energy-efficient designs has never been so challenging ... or so critical. No wonder power engineers everywhere turn to Fairchild. The Power Franchise offers more power-efficient solutions and support services across a broader range of designs than anyone.

### Advanced technologies inside, leading packaging outside

Leveraging innovative process technologies across power analog, power discrete and optoelectronics products from 1W to 1200W, Fairchild provides the industry's most comprehensive portfolio of standard components and application-optimized ICs. The result? Solutions that maximize energy savings in power-sensitive applications.

#### More ways to optimize your designs

Improving energy efficiency is one of many ways Fairchild can help to optimize your designs. For example, our overall component performance and functional integration reduce board space, design complexity and system cost. And with online tools, FAEs and regional centers staffed by PhD-level power engineers, our Global Power Resource™ represents the industry standard in customer design support.

### Satisfy regulatory requirements and exceed customer expectations

Around the globe, discover how Fairchild's power designs can help you meet the most demanding energy efficiency regulations and OEM application requirements.

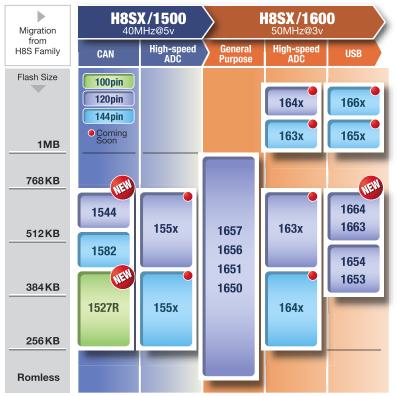

#### H8SX - 32-bit CISC, Single cycle, Powerhouse

Up to 1MIPs/MHz, fast multipliers/dividers, zero wait state Flash

#### **Renesas Technology**

#### No. 1\*1 supplier of microcontrollers in the world

introduces the high-performance H8SX Series of microcontrollers. Upwardly compatible with the popular H8 architecture, the 32-bit, 50MHz H8SX CPU core provides the performance needed for the next generation of products.

A comprehensive array of peripherals, including USB and other advanced data management functions, gives full system integration. H8SX integrated peripherals and high-speed I/O combine to provide a MCU with advanced performance in every clock cycle.

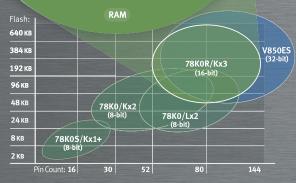

#### **H8SX Product Roadmap**

\*1Source: Gartner Dataquest (April 2006) "2005 Worldwide Microcontroller Vendor Revenue" GJ06333

#### **Get Started Today -**

Go online and register to be eligible for a FREE Starter Kit

www.america.renesas.com/ReachH8/a

Renesas Technology Corp.

# ANALOG edge<sup>ss</sup>

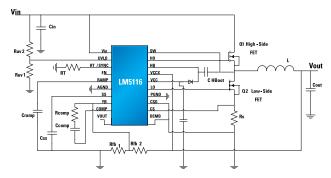

#### Minimizing FET Losses for a High-Input Rail Buck Converter

#### **Application Note AN-1628**

William Stokes, Applications Engineer

Engineers often face the challenge of choosing the input voltage rail that works best for the DC-DC converter at the Point-of-Load (POL). High voltage rails, above 12V, usually demand intermediate regulation stages that reduce overall efficiency and add to cost. However, the new generation of regulator and controller ICs afford POL regulation from these high input rails directly. Typically the buck regulator is employed as the POL workhorse but its efficiency is highly dependent on the optimization of the High-Side (HS) and Low-Side (LS) MOSFET (FET) combinations. At lower input voltages it is often possible to use the same HS and LS FETs, yet for higher input voltages the selection criteria for these FETs are different, and will be the subject of this application note.

#### **Buck Converter Loss Mechanisms**

The schematic in *Figure 1* shows the basic architecture for a DC-DC buck (or step-down) voltage regulator circuit that employs the LM5116 as the Pulse Width Modulator (PWM) switch controller. The critical current path is from  $V_{\rm IN}$  through the HS FET to the output via the inductor; and alternately, from ground through  $R_{\rm S}$  and the LS FET to the output. Power losses due to the FETs along this path tend to dominate all other losses.

Figure 1. Synchronous Buck Regulator Schematic

Losses occurring in the FETs are a combination of conduction losses in the channel of the FET and switching losses during the turn-on and turn-off transitions. Conductive losses are proportional to the RMS current through each FET, and ignoring the ripple current in the output inductor, are often approximated (for the HS and LS respectively) by the following:

$$\begin{split} P_{OHS} &= I_{OUT}^2 \cdot R_{DHS} \cdot D \text{ and} \\ P_{OLS} &= I_{OUT}^2 \cdot R_{DLS} \cdot (1-D) \quad \text{(Eq. 1)} \end{split}$$

In these equations  $I_{OUT}$  is the output current,  $R_{DHS}$  and  $R_{DLS}$  are respectively the on-resistances of the HS and LS FETs, D is the duty cycle of the HS FET and (1-D) is the duty cycle of the LS FET.

The duty cycle, D, is given by  $D = \frac{V_{IN}}{V_{OUT}}$  (Eq. 2)

The switching behaviors of the HS and LS FETs in the buck regulator differ from each other and this difference can be understood with the aid of *Figure 2*.

Figure 2. Basic Switching Characteristics (not to scale) for HS and LS FET Operating in a DC-DC Converter Application

The LS FET exhibits zero-voltage switching. First of all, the gate voltage,  $V_{LSgate}$ , turns the FET on while the FET's body diode is conducting. Then, when the gate turns the FET off, the load current will continue to flow in the same direction but now through the body diodes, such that the drain voltage stays near zero. Thus the attendant switching losses are negligible in both cases.

The main switching loss caused by the LS FET occur in the gate driver due to the charging and discharging of its gate capacitance. At higher frequencies in high power systems this can impose an upper limit on the number of LS FETs that can be used in parallel to reduce the onresistance. The increase in gate drive power required as more FETs are used in parallel can exceed the reduction in conduction losses.

Switching losses are significant in the HS FET because its drain-source voltage is equal to  $V_{IN}$  and its drain current is approximately equal to  $I_{OUT}$  at both turn on and

The switching losses are approximated by  $Psw_{QI} = \frac{1}{2} \cdot V_{in} \cdot I_{out} \cdot f_{sw} \cdot (tsw_{HS\_rise} + tsw_{HS\_fall}) + Q_{gs} \cdot V_{GH} \cdot f_{sw} + \frac{1}{2} \cdot C_{oss} \cdot V_{in}^{i2} \cdot f_{sw}$

where  $f_{SW}$  is the switching frequency;  $tsW_{HS\_rise}$  is the time it takes the gate voltage to rise from its threshold value to the end of the plateau interval;  $tsW_{HS\_fall}$  is the time it takes the gate voltage to fall from the beginning of the plateau interval to the threshold value;  $Q_{gs}$  is the total gate charge of the FET;  $C_{oss}$  is the FET's drain-source capacitance; and  $V_{GH}$  is its gate drive voltage. The determination of the fall and rise times is beyond the scope of this article, but the relevant equations can be found in the web-published application notes of various MOSFET vendors.

turn off, leading to large overlap losses.

The first term on the right hand side in *Eq. 3* is the power lost in the FET due to the simultaneous high drain current and drain-source voltage at turn on and off already mentioned. The second term is the power required by the FET's gate, (which is dissipated in the gate driver). The third term is the power dissipated in charging the parallel combination of the LS and HS FETs' output capacitance.

Another switching loss that occurs in the HS FET is due to the reverse recovery of the LS FET's body diode. This loss can be virtually eliminated at low currents (<5A) by paralleling a schottky diode with the LS FET.

#### **Design Lessons**

The following generalizations are based on the above equations and should give further insight into FET selection:

- Switching losses increase for larger gate and drain capacitance and these capacitance are inversely proportional to the on-resistance. FETs with the lowest on-resistance inevitably have the higher capacitance hindering HS switching speed.

- 2) Reducing the switching clock frequency reduces switching losses; that is, at lower frequencies the losses during on/off transitions become a diminishing proportion of the total on-time of the FET causing conduction losses to increasingly dominate.

- 3) For higher input voltages relative to the output voltage the duty cycle of the HS FET decreases causing the switching losses to increasingly dominate.

- 4) In order to further reduce conduction losses, multiple, parallel, LS FETs are often employed. The number of parallel FETs is determined ultimately by cost,

the gate driver's ability to drive them, and the point of diminishing returns.

The engineer should be aware that in most POL applications, especially for input voltages higher than 12V, the switching losses will likely dominate all other losses. Equation 3 shows that under these circumstances the lowest overall losses in the HS FET are not necessarily achieved by using a device with the lowest on-resistance. The FET must be selected to minimize the sum of all the losses. The FET's on-resistance must be optimized at a higher value to achieve reduced capacitance and so reduce the switching losses. The major MOSFET vendors now provide "reduced charge, fast switching "MOSFETs which are optimized in this way for high-side buck applications.

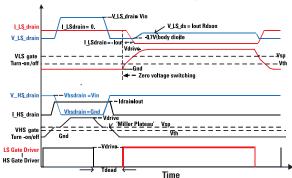

Figure 3. DC-DC Converter Measured Data Showing the Efficiency as a Function of the Switching Frequency

If optimizing the FETs does not enable high enough efficiency in a system, the switching frequency can be reduced to decrease the switching losses and improve the efficiency. This, however, can result in a physically larger system. Figure 3 is an example of measured data from a generic evaluation board. The efficiency of this board was measured at various switching frequencies without changing any components on it except for the frequency-setting resistor. Though the conduction losses increased as the switching frequency was reduced (due to increased ripple currents), the overall efficiency went up because the switching losses in the HS FET decreased. The graph shows that changing the switching frequency has a dramatic effect on the switching losses.

The foregoing discussions have made clear that to achieve maximum efficiency in a high input voltage buck converter, the high side MOSFET must be carefully selected to minimize the sum of the switching and conduction losses.

The author wishes to acknowledge Haachitaba Mweene for his help with writing this article.

National Semiconductor 2900 Semiconductor Drive Santa Clara, CA 95051 1 800 272 9959

Mailing Address: PO Box 58090 Santa Clara, CA 95052

#### EDN

#### PUBLISHER. EDN WORLDWIDE

Alan Robinson 1-408-345-4450; fax: 1-408-345-4400; aarobinson@reedbusiness.com

#### EDITORIAL DIRECTOR, EDN WORLDWIDE

Maury Wright, 1-858-748-6785; mgwright@edn.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-408-345-4427; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR Kasey Clark

1-781-734-8436; fax: 1-781-290-3436; knse@reedbusiness.com

#### EDITOR IN CHIEF, EDN.COM

Matthew Miller

1-781-734-8446; fax: 1-781-290-3446; mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary

1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994: naul.rako@reedbusiness.com

#### EDA, MEMORY, PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor 1-408-345-4424; michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPs, TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-781-734-8070; rcravotta@edn.com

#### MASS STORAGE, MULTIMEDIA, **PCs AND PERIPHERALS**

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-781-734-8038; bdipert@edn.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242: fax: 1-805-461-9640: mconner@reedbusiness.com

#### DESIGN IDEAS EDITOR

Charles H Small edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-781-290-3439;

f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-347-9605; mbutler@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION MANAGER

Diane Malone, Manager 1-781-734-8445; fax: 1-781-290-3445 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-781-290-3442 Melissa Annand, Newsletter/Editorial Coordinator Contact for contributed technical articles 1-781-734-8443; fax: 1-781-290-3443 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-781-290-3325

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD: Bonnie Baker; Joshua Israelsohn; Pallab Chatterjee

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager 1-781-734-8328: fax: 1-781-734-8086

Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### FDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu. Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.ip Kenii Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.jp Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.ip

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### **DENNIS BROPHY**

Director of Business Development, Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV System Architect, Intel

RON MANCINI

Retired Staff Scientist GARRIEL PATULEA

#### Design Engineer, Cisco

#### DAVE ROBERTSON

Product Line Director, Analog Devices

#### SCOTT SMYERS

VP Network and System Architecture Division, Sony

#### TOM SZOLYGA

Program Manager, Hewlett-Packard

#### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fax 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@ reedbusiness.com. For a free subscription, go to **www.geffreemag.com/edn**. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

Our 16-bit MCUs give you tons of options in every area but one.

### They only come in black.

#### 78K0R/Kx3 16-bit MCUs

| Flash: |                |       |       |       |       |

|--------|----------------|-------|-------|-------|-------|

| 512 КВ |                |       | 30 кв | 30 кв | 30 KB |

| 384 кв |                |       | 24 КВ | 24 КВ | 24 KB |

| 256 кв | 12 KB          | 12 KB | 12 КВ | 12 KB | 12 KB |

| 192 кв | 10 кв          | 10 кв | 10 кв | 10 кв | 10 кв |

| 128 кв | 8кв            | 8кв   | 8кв   | 8кв   | 8кв   |

| 96 кв  | 6кв            | 6 КВ  | 6кв   |       |       |

| 64 кв  | 4кв            | 4кв   | 4кв   |       |       |

| Pin Co | unt: <b>64</b> | 80    | 100   | 128   | 144   |

#### More choices in on-board flash.

NEC Electronics America makes it easy to get exactly what you want. Our microcontrollers give you strength in memory, power and performance. The 78KOR product lineup includes 30 devices available in 64 to 144 pins and 64 KB to 512 KB of memory—the widest range of on-board flash memory available. Compared to the leading 16-bit solutions available, these MCUs will save you 30% or more on power consumption. They deliver 13 Dhrystone MIPS at 20 MHz. Plus, migration from our 8- to 32-bit microcontrollers is simple — even the colors are compatible.

Learn more at <a href="www.am.necelcom/16bitmcus">www.am.necelcom/16bitmcus</a> and order a FREE starter kit while supplies last. Restrictions apply.

NEC

#### Blade computer sports four cores

iming to boost the performance of applications in the telecommunications, medical-engineering, and transportation industries, MEN Micro recently released a new 6U, CompactPCI single-board computer featuring either one or two Intel Xeon dualcore processors operating at 1.66 GHz. You can use the hot-swappable D7 server blade as a peripheral-slot board; a 64-bit, 66-MHz PCI system board; or a 64-bit, 133-MHz PCI-X (PCI Extended) system board. The D7 allows multiple memory variants, including error-correcting DRAM, nonvolatile FRAM (ferroelectric random-access memory), SRAM, and NAND flash. The built-in PCI Express link drives the two Gigabit Ethernet interfaces on the front panel and one or two XMC (switched-mezzanine-card) modules. The D7 also supports 12-Gbps Ethernet connections without performance losses.

In addition to a front-panel USB slot, the D7 includes two serial and two parallel ATA

The new D7 CompactPCI single-board computer features dual-core processors, hot-swap functions, and a reconfigurable I/O section.

(Advanced Technology Attachment) interfaces for connection of mass-storage devices or CompactFlash. The D7 includes an FPGA for configuration of application-specific I/O functions, such as additional serial interfaces, graphics, fieldbus interfaces, and digital I/O. The price for the D7 is \$5010, and delivery is within two weeks after receipt of order.

-by Warren Webb

▶ MEN Micro Inc. www.menmicro.com.

#### ■ FEEDBACK LOOP

"I had a hi-fi nut for a housemate a few years back. ... Unlike many, he didn't fall for the whole OFC (oxygen-free-copper) thing. Instead, he braided three or four pieces of multistrand, copper-mains-rated cable to produce flat, flexible cables. ... (It's) simple, safe, cheap, good listening ... can't get better than that!"

-Dean Perry, in EDN's Feedback Loop, at www.edn. com/article/CA6418215. Add your comments.

#### Synchronizable POL converters beat the noise

Power subsystems that use a DPA (distributed-power architecture) usually have several independent power modules throughout the system, providing different voltages and currents and probably switching at different frequencies. These differing frequencies can cause significant noise problems for the system. The IBA (intermediate-bus architecture) is even more susceptible to module switching noise. It has more switching modules with higher switching currents resulting from the lower voltages of the architecture's nonisolated POL (point-of-load) converters. Add to this the fact that the power subsystems often mix power converters from different manufacturers, and a very noisy power environment can result.

To address these problems, the NAT1vvvvXcc family of POL converters from NetPower includes a synchronization option to allow all POL converters in a system to operate at the same switching frequency and to eliminate beat frequencies. In addition, you can phase-shift the converters' clocks, allowing the converters to operate in an interleaved mode and further reduce switching-frequency noise. The synchronization also lets designers avoid critical frequencies that may interfere with the system's operation or modulate the switching frequency to eliminate or manage system EMC (electromagneticcompatibility) problems. The input range for the modules is 8.5 to 18V, and the output range is 0.75 to 8V with a 12A (\$9.30) or a 20A (\$11.50) output current.-by Margery Conner

NetPower, www.netpowercorp.com.

The NAT1vvvvXcc family of POL converters from NetPower includes a synchronization option to allow all POL converters in a system to operate at the same switching frequency and to eliminate beat frequencies.

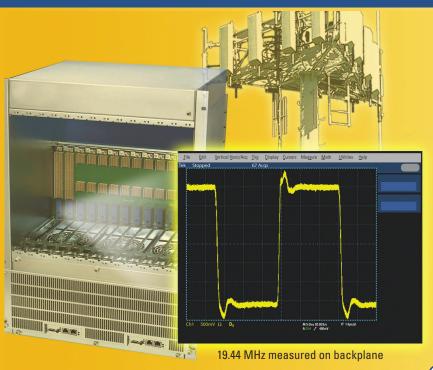

#### 100M-sample/sec, 14-bit digitizer and 25- and 50-MHz digital-I/O modules are first to support PXIe

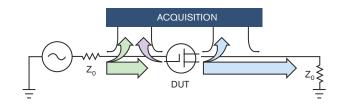

ational Instruments has announced what it calls the industry's first PXIe (PXI Express) highspeed instruments as well as the industry's first 18-slot PXIe chassis. The modular instruments include the 100-MHz, 100M-sample/sec, dualchannel PXIe-5122 digitizer and the 50- and 25-MHz, 32channel PXIe-6537 and PXIe-6536 digital-I/O modules. The PXIe-1065's 18-slot chassis offers dedicated bandwidth of as much as 1 Gbyte/sec per slot and both PXI and PXIe slots. According to the company, the PXIe products target applications such as signal

intelligence, spectral monitoring, semiconductor-chip characterization, and video test.

"PXIe builds on commercial PCIe [PCI Express] technology to increase the number of applications the multivendor PXI standard serves," says Eric Starkloff, National Instruments' director of test-product marketing. "Adding a high-speed data-streaming capability to PXI maintains the compatibility among more than 1200 modules from more than 70 vendors that has made the standard a leading modular-instrumentation platform."

The new instruments add to the manufacturer's extensive list of PXI mixed-signal products, which include high-speed digitizers and oscilloscopes, high-speed digital-I/O modules, baseband and RF analyzers, and signal generators. The new instruments enable high-speed data recording and playback through the newest industry-standard bus, PCIe, which, on a bidirectional, fourlane link, delivers as much as 1 Gbyte/sec of streaming throughput. For example, with the four-lane-link-based PXIe-5122 digitizer, you can simultaneously capture analog signals on two channels with 14-bit resolution at 100M samples/sec and stream the signals across the PCle bus to the PC's memory or hard disk at the digitizer's full rate of 400 Mbytes/sec. You can also use the X1-link-based PXIe-6536/37 digital-I/O modules to stream digital waveforms to and from the module at the full 200-Mbyte/sec data rate.

The PXIe-1065's 18-slot chassis complements the PXIe-1062's eight-slot chassis to address higher-channeldensity PXIe-based systems. The new chassis includes a combination of PXI and PXIe hybrid slots to accept both current PXI modules and higher bandwidth PXIe modules. All of the PXIe products integrate with a variety of software, including the manufacturer's LabView graphical-development environment, LabView SignalExpress interactivemeasurement software, and TestStand test-management software.

Prices for the PXIe-5122 digitizer, the PXIe-6536/37 digital-I/O modules, and PXIe-1065 chassis start at \$5499, \$1799, and \$5499, respectively.-by Dan Strassberg

National Instruments. www.ni.com.

The PXIe-6537, which interfaces through a one-lane PCle high-speed, bidirectional serial bus, accepts 32 channels of digital I/O with data rates as high as 50 MHz per channel.

#### **DILBERT By Scott Adams**

#### AC/DC SUPPLY **ACHIEVES** 11.2W/IN.3

The MFA350 ac/dcpower supply from XP Power provides 350W in its  $3.2 \times 6.8 \times 1.5$ -in.  $(81\times173\times38\text{-mm}), U$ bracket package. The base product delivers 364W across the entire input range of 90 to 264V ac and is available in 12, 24, and 48V-dc-output versions. It includes a 12V, 1A fan supply and a 5V, 0.3A standby supply and signal set, including ac fail, dc OK, remote on/off, active current sharing, and remote sensing. The unit functions at full power from -10 to  $+50^{\circ}$ C and at temperatures as high as 70°C with derating. The MFA350 is 89% efficient and requires 13cfm airflow for full output power. Hot-swap models have ORing FET outputs, front-access IEC (International Electrotechnical Commission) inlets, and extraction handles. The supply fits a 1U×2U profile, allowing vertical or horizontal orientation in a standard telecom chassis. It costs \$175 (OEM

-by Margery Conner XP Power, www. xppower.com.

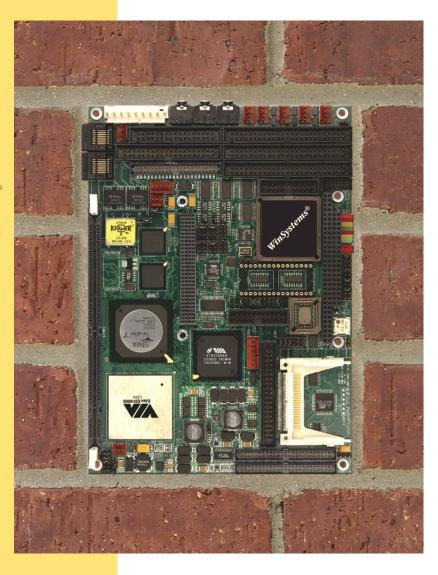

### **BUILT TO LAST**

#### Fanless EBX 733MHz P3 with COM, dual ENET, **USB** and Video

- VIA 733MHz or 1GHz C3 CPU

- PC-compatible, supports Windows® XP, CE, Linux and x86 RTOS

- Up to 512MB PC133 SDRAM

- Up 1GB bootable DOC<sup>®</sup>, 512KB SRAM, or 1MB EPROM

- Type I and II CompactFlash cards supported up to 8GB

- CRT, flat panel, and LVDS

- Two 10/100 Ethernet controllers

- Four USB ports

- Four serial COM ports

- LPT, Kybd, and mouse

- 48 bi-directional I/O lines

- Two EIDE and one floppy disk controller

- AC97 Audio supported

- PC/104 & PC/104-Plus expansion

- +5 volt only operation

- EBX size: 5.75" x 8.0" (146 mm x 203 mm)

- -40° to +85°C operation (733MHz)

- Quick Start Developers Kits for Windows® XP, CE, and Linux

- Immediate availability

The EBC-C3 embeds 9 different functions to provide a processor- and I/O-intensive solution. It operates over a -40° to +85°C temperature range without the need of a fan, making it ideal for embedded applications such as robotics, MIL/COTS, transportation, pipeline, and machine control.

It runs Windows® CE, Windows® XP embedded, Linux, and other operating systems as VxWorks and QNX. And its x86-PC software compatibility assures a wide range of tools to aid in your application's program development and checkout.

Call 817-274-7553 or Visit www.winsystems.com

Ask about our 30-day product evaluation!

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

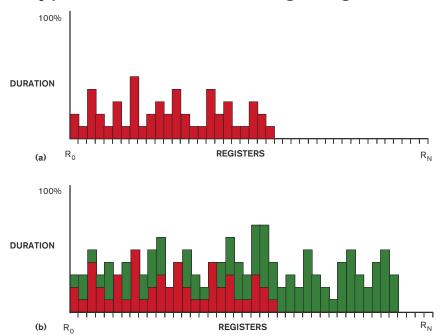

#### Calypto fields RTL-clock-gating tool

PowerPro CG finds more clock-gating opportunities and gates logic for longer times. In original designs, customers achieved efficiencies of 62.6 and 39.1% without PowerPro CG (a). Using the tool, the same customers achieved, respectively, 72.8 and 61.8% efficiency (b).

DA start-up Calypto Inc has broadened its product portfolio beyond system-to-RTL (register-transfer-level) functional-verification tools with the introduction of an automated clock-gating tool for low-power-IC design. The PowerPro CG (clock-gating) tool complements the company's SLEC (sequentiallogic-equivalence checker) CG, RTL, and other functionalanalysis tools. PowerPro CG aims to help design engineers create low-power designs. The company claims that, using the tool, beta customers that were previously performing manual clock gating on their designs further reduced dynamic-power consumption by as much as 60%.

Tom Sandoval, chief executive officer of Calypto, says that one of the most popular ways that engineering teams

reduce power consumption in IC designs is to gate clocks, but designers traditionally do most of the gating late in the design process at the gate level during layout; as a result, they must manually perform this task. With PowerPro CG, Calypto hopes to change that situation. The analysis-driven PowerPro CG allows designers to reduce dynamic power without impacting leakage power, area, or timing, according to Sandoval.

Designers will use the PowerPro CG with logic synthesis. They run the RTL versions of their designs in synthesizable Verilog or VHDL through synthesis to get a power figure. They then feed the raw RTL, an SDC (Synopsys Design Constraint) timing file, an SAIF (Switching Activity Interchange Format) file, and a Liberty Synopsys cell-li-

brary file to the PowerPro CG. The tool analyzes the RTL for clocks that designers can gate for further power savings. Users can select which clocks they want the tool to gate and select critical paths they don't want the tool to gate. The tool then analyzes the RTL and generates power-optimized RTL for the selected clocks. Users can then run SLEC CG

to ensure that the power-optimized version of the RTL is functionally the same as the original RTL. Users can also then run the power-optimized RTL through logic synthesis.

The tool performs power optimization with no impact on timing, and, in most cases, the optimization reduces the overall die area the design reguires. The tool takes advantage of the company's SLEC sequential-analysis engine, finding opportunities to reduce power that manual inspection misses. "If engineers spend enough time inspecting RTL and analyzing how it works sequentially, they can come up with these same transforms," says Sandoval. "But that task would be very difficult." He notes that, for efficient clock gating, a tool or an engineer must consider which logic to gate and for how long and then must consider the tradeoff of gating versus area or performance.

"PowerPro optimization typically finds hidden opportunities for gating and opportunities to gate more obvious clocks for a longer period of time," says Sandoval. PowerPro CG runs under Linux and sells for \$295,000 for an annual subscription.

−by Michael SantariniCalypto, www.calypto.com.

#### **FEEDBACK LOOP**

"Engineers not only trade value for money, but also provide an opportunity for others to participate. As an engineer in an upstart, I have come to realize that there are dozens of people employed because I offered that trade, and there are hundreds of others that purchase my product and, through that, many more people are afforded a livelihood."

—Kevin Kilzer, in *EDN*'s Feedback Loop at www.edn.com/article/CA6409623.

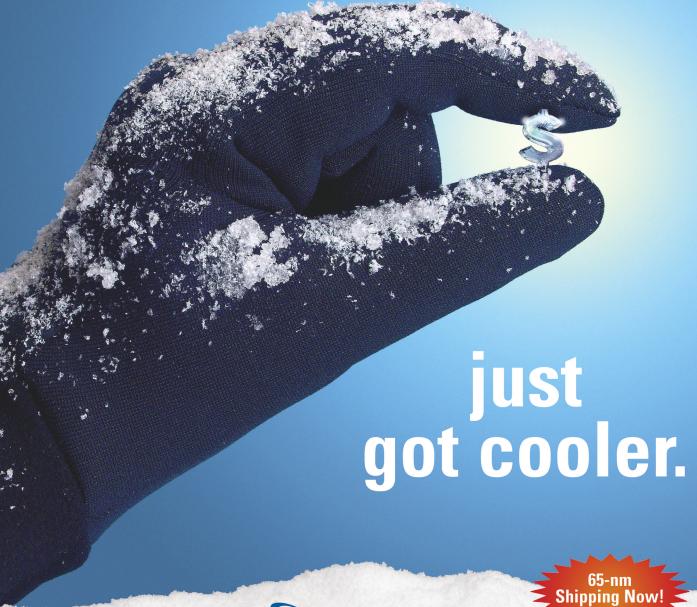

# Cyclone economics

Cool down your system with the industry's first 65-nm, low-power, low-cost FPGAs. The Cyclone® III family provides an unprecedented combination of power, functionality and cost, helping turn your ideas into revenue.

Design with Cyclone III FPGAs. Your possibilities are unlimited.

Copyright © 2007 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights.

# Atmel's AVR32 UC3 processor boasts low power

t last month's Embedded Systems Conference in San Jose, CA, Atmel announced the AVR32 UC3 core and the UC3 Series A microcontrollers. Atmel is aiming the devices at designers considering ARM's (www. arm.com) ARM7, ARM9, and Cortex-M3 processors. Atmel claims that the UC3 Series A microcontrollers deliver 80 Dhrystone MIPS and consume only 40 mA at 66 MHz when operating from a 3.3V power supply.

The AVR32 UC3 integrates SRAM in a three-stage-pipeline, dual-bank architecture to bypass the system bus to achieve faster execution, cycle determinism, and lower power consumption. An HSB (highspeed-bus)-slave-interface access allows DMA controllers or other HSB masters to write to or read data directly from the closely coupled SRAM. The unit performs arbitration if the CPU and a high-speed slave simultaneously request access, and the priority scheme is programmable to suit application needs. No data hazards exist in the UC3 core pipeline, so the device can update register files during the same clock cycle as instruction execution.

The core is the second that Atmel derived from the AVR32 AP architecture. The 32-bit RISC core has instruction extensions that add DSP instructions to the instruction set of the original core. The DSP instructions include single-cycle MAC (multiply-accumulate) operations covering standard and fractional numbers with and without saturation and rounding and with 32- to 64-bit results. Additional DSP in-

structions include data-formatting instructions, such as data shift with saturation and rounding.

The ISA (instruction-set architecture) permits freely intermixing 16- and 32-bit instructions. The core shares the ISA as its AVR32 AP parent, with more than 220 instructions available as 16-bit compact and 32-bit extended instructions. Load/store instructions support byte (8-bit), half-word (16-bit), word (32-bit), and double-word (64-bit) data

The microcontrollers deliver 80 Dhrystone MIPS and consume only 40 mA at 66 MHz.

types. The AVR32 ISA has instructions to modify data from the register file before storing it in memory and from memory before storing it in the register file. On-the-fly data manipulations include load-and-insert bit fields, load and swap, and store and swap. The UC3 ISA includes atomic instructions to manipulate mutexes and semaphores and for general bit manipulation.

The core includes powermanagement functions; a memory-protection unit; and a six-level priority-interrupt controller, including NMI (nonmaskable interrupt) with fast event handling. The core's event-handling system support NMI; exceptions, such as illegal operating codes and bus errors; and four interruptpriority levels. The first instruction from the event handler executes within 12 clock cycles from an autovectored-handler address. To limit the maximum interrupt latency to 16 clock cycles, pending interrupts can abort multicycle instructions.

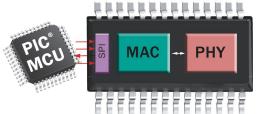

UC3 Series A microcontrollers include a peripheral DMA controller, a multilayer HSB architecture, a 10/100-Gbps Ethernet media-access controller, an ADC, two master/slave SPIs (serial-peripheral interfaces), one SSC (synchronous serial controller), a TWI (two-wire interface), four USARTs with hardware flowcontrol, and full-speed USB OTG (On-The-Go). The microcontrollers are available with an EBI (external bus interface) that extends the addressable physical memory to 16 Mbytes. Its nonmultiplexed, 16-bit data bus can interface to high-density external SRAM; SDRAM; ROM; flash devices; and memory-mapped devices, such as LCDs and FPGAs. The devices include three 16-bit timers and seven PWMs (pulse-width modulators) that can trigger the 10-bit, eight-channel ADC to ease electrical-motor-control desian.

The on-chip system manager includes an internal voltage regulator for 3.3V single-power-supply operation, power-on reset, a brownout detector, a hardware watchdog timer, and a real-time timer. The clock system provides an on-chip RC oscillator; two high-frequency external oscillators; one 32-kHz oscillator; and two independent, on-chip PLLs. Special security options are available to protect the flash contents. The device consumes 40 µA in sleep

mode and  $600~\mu\text{A/MHz}$  in active mode. You can switch off any section of the UC3 Series A device that is not in use by disabling its clock. The core uses a multithreshold-transistor library to reduce static-power consumption.

Atmel provides free software, including the GNU gcc C compiler, GNU gdb debugger, FreeRTOS.org real-time kernel, and IwIP TCP/IP (Transmission Control Protocol/Internet Protocol) stack for the family. Atmel's AVR32 Studio and AVR JTAGICE mkll, along with the company's 8-bit AVR microcontrollers, provide the AVR32 UC3 with a multiplatform IDE for the GNU tool chain, including support for more advanced debugging sessions with data and code trace using the AVR32's Nano Trace. The AVR32 UC3 has a Nexus Class 2+ interface through the auxiliary port, providing access to more powerful debugging features, including nonintrusive data and program trace. The EVK (evaluation kit) 1100 is available to support the devices. It includes Ethernet and USB interfaces, as well as SPI, TWI, and USART serial-communications ports. A 20×4-character LCD and the expansion connector allow advanced product evaluation and prototyping activities.

The two first devices of the UC3 Series A are available for sampling now and will be available in volume production in the fourth quarter of 2007. The AT32UC3A0512, with an EBI and 512 kbytes of flash, is available in a QFP144 for \$8.16 (10,000). The AT32UC3A1512, without an EBI and 512 kbytes of flash, is available in a QFP100 for \$7.43 (10,000).

−by Robert Cravotta

Atmel, www.atmel.com.

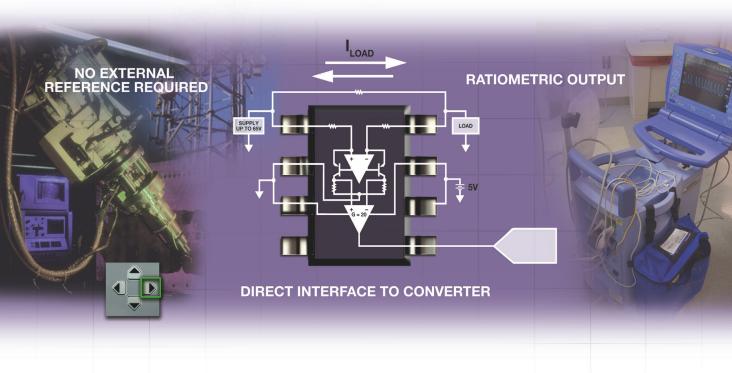

# Bidirectional current monitors that make sense. In measurement and control, analog is everywhere.

#### AD8210 Bidirectional Current Sense Amplifier

- −2 V to +65 V operating common-mode voltage range

- −40°C to +125°C operating temperature range

- 120 dB typical CMRR at dc

- 10 ppm/°C typical gain drift

- Gain of 20

- 500 kHz bandwidth

- Price: \$1.79/1k

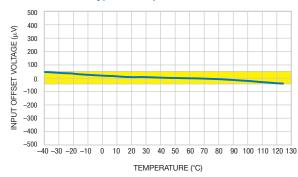

#### Typical $\leq 1 \mu V/^{\circ}C$ Offset Drift

#### Precision over temperature—guaranteed

With our new AD8210 bidirectional current sense amplifier, you get the industry's most integrated, flexible, and accurate current sense monitor. With features like  $\pm 8~\mu\text{V/°C}$  maximum offset drift and 20 ppm/°C maximum gain drift guaranteed across the entire  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  temperature range, it represents a milestone in precision current sense monitoring. The AD8210 improves your ability to meet your error budget and to control more precisely a wide range of loads in communications, industrial, and medical applications. Two other bidirectional monitors—the AD8205 (gain of 50 V/V) and the AD8206 (gain of 20 V/V)—offer 50 kHz operation and excellent performance over temperature.

All three amplifiers feature an innovative ratiometric output offset architecture that inherently improves the accuracy of your ADC and your system. With a typical 5 V single-supply, each device can be configured for both bidirectional and unidirectional current sensing. Excellent output accuracy is maintained throughout the input voltage range through the use of a proprietary thin film precision network.

For more information on ADI's current sense amplifiers and monitors, please visit *www.analog.com/currentsense* or call 1-800-AnalogD.

#### **MRESEARCH UPDATE**

BY RON WILSON AND MATTHEW MILLER

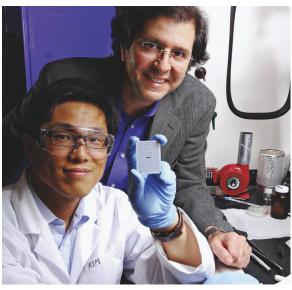

Researcher Philseok Kim (left) and Professor Joseph Perry (right) display a capacitor array fabricated using a new nano-encapsulated dielectric material.

#### Nanocomposites promise advance in thin-film electronic components

esearch at the Georgia Institute of Technology Institute for Organic Photonics and Electronics has demonstrated a technique for using nanofabrication principles to employ a powerful, but hitherto intractable, dielectric material in thin-film capacitors and, potentially, transistors. The material, barium titanate, has long been known to have a high dielectric constant. But the substance tends to clump when suspended in a polymer, creating large granules that exhibit very low breakdown voltage.

The Georgia Tech team, led by Professor Joseph Perry, tried nano-encapsulation to tame the clumping and create a uniform dispersion of the barium titanate in the polymer matrix. To achieve this goal, Perry's team turned to a second group, led by Professor Seth Marder, to synthesize a designer phosphonic-acid ligand that would both bond securely to the barium titanate and form a capsule compatible with commonly used thin-film polymers. The resulting capsules range from 30 to 120 nm in diameter, as much as four times smaller than granules researchers have fabricated using conventional means. The smaller encapsulated particles also proved friendly to the host polymers, achieving uniform dispersion and hence yielding thin-film capacitors with as much as twice the capacitance per unit area of previous attempts. Perry sees further application in gate dielectrics for thin-film field-effect transistors.-RW

**⊳Georgia Institute of** Technology, www.gtresearch news.gatech.edu.

#### NEC plastic cools the palm and the earth

new carbon-fiber-enhanced plastic material from NEC Research has the potential to both more evenly spread heat in the enclosures on electronic devices, such as cell phones, and to help global warming. The material is made from more than 90% biomass material; you can't get much greener than that.

The material is formed using a specially developed binder-literally, a secret sauce-in a PLA (polylactic-acid) resin. The action of the binder causes carbon fibers suspended in the resin to crosslink, forming a web of heat-conducting fibers. When formed into the case on an electronic device, such as a cell phone, this cross-linked web conducts heat laterally, away from hot spots on the package, as well as vertically, through the case, at rates in excess of the conductivity of stainless steel. Thus, the package can cool itself without

causing uncomfortable hot spots on the surface above heat-generating components.

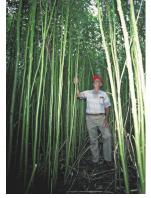

The material's green credentials are impeccable. NEC is making the PLA resin-a polymerized lactic acid-by fermentation of kenafa super-fast-growing, carbon-dioxide-voracious African/Asian plant related to cotton. NEC researchers have succeeded in getting the kenaf-derived PLA to have good molding properties, high heat resistance, and compatibility with the company's special binder.-RW

The kenaf plant may be the future of plastic enclosures for handheld electronics.

▶NEC, www.nec.co.jp/rd/rel/ english/topics/t38.html.

#### **ENERGY HARVESTER GENERATES CONTINUOUS** NANOAMPERE CURRENT

Researchers at the Georgia Institute of Technology have created a tiny device that produces a direct current by harnessing the piezoelectric output of hundreds of swaying zinc-oxide nanowires. Buffeted by

A tiny device produces a direct current by harnessing the hundreds of swaying

ultrasonic waves or mechanical vibration, the device features a forest of vertically oriented nanowires, whose tips lie in the valleys of a peak-and-valleyshaped electrode. As the wires flex, they periodically contact an electrode and transfer their electrical charge. A prototype device produces current in the nanoampere range, but the researchers claim the technology can scale to produce 4W/cm<sup>3</sup>.-MM

Georgia Institute of Technology, www.gatech.edu.

### A series of engineering insights by Analog Devices.

#### **Solving Dynamic Range Problems in Analog Systems**

Many of the applications that we take for granted operate in real-world environments with high levels of dynamic range. The most common of these systems are radio and television receivers and their updated cousins—the cell phone and the iPod. The signal range for these types of household devices can vary from a few microvolts in remote areas to volts when the device is near the signal source. Situations with wide dynamic range are also found in scientific, industrial, and medical applications—such as the "front ends" of measurement equipment,

ultrasound imaging for biological diagnostics, and industrial fault analysis. Designers have been faced with the dual challenges of providing the highest sensitivity amplifiers possible while at the same time making them operable under severe overload conditions.

In the early days of electronics, solutions to these challenges were sought by "tinkering" with the amplification devices. In the case of vacuum tubes, this involved adding control grids within the tube structure to alter the conductivity and thus, the gain of the device. For transistors, electronic gain

control was limited to adjusting the dc base or emitter currents. While these solutions were relatively successful, they typically compromised linearity and distortion performance. A more viable solution had to wait until the advent of highly complex integrated circuits in the late 1980s, when Analog Devices invented and introduced the AD600—the first solid-state variable gain amplifier (VGA) to operate in a linear manner.

This amplifier was also called the X-amp or exponential amplifier. The advantages of this device lie in its architecture—a passive electronic gain control implemented with a resistive ladder network and followed by a fixed-gain amplifier. There are six to eight "rungs" on the ladder, connected to an "interpolator circuit" that sweeps across the ladder in response to an externally supplied control voltage. This concept has been the basis for many subsequent products that offer additional features and enhanced performance. However, the basic gain-control architecture has not changed.

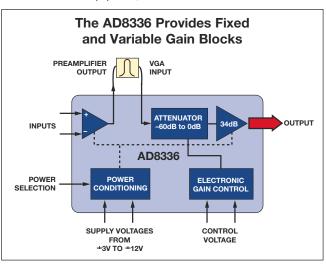

The AD8336 is one of several newer solutions in Analog Devices' VGA portfolio. This device offers an industry-leading balance of size, performance, and circuit versatility while operating across wide power supply voltage and dissipation ranges.

The versatile AD8336 variable gain amplifier features an uncommitted, fully independent voltage feedback op-amp to which ac- or dc-coupled signals of either polarity can be applied. The preamplifier output

can be applied directly to the VGA input—or interstage selectivity or filtering can be inserted between the preamplifier and VGA. The preamplifier can be connected as a summing stage or differentially like any high frequency op amp—enabling fast, convenient interconnection to virtually any signal source.

Just as the preamplifier is capable of differential connections, so too is the gain control input. The input may be ground referenced or connected from a reference supply appropriate to the gain control

source. This capability is particularly useful with cascading devices. For higher voltage applications, the device may be operated from supplies as high as  $\pm 12$  V or as low as  $\pm 3$  V for battery operation. To conserve battery life, the power may be reduced by approximately 50% at the expense of bandwidth.

Analog Devices offers an extensive portfolio of variable gain amplifiers for applications such as ultrasound, radar, and wireless communications. For data sheets, free samples, and additional information, please visit www.analog.com/LI-VGA or call 1-800-AnalogD. ▶

Author Profile: **James Staley** is an applications engineer in the Integrated Amplifier Products Group at Analog Devices.

#### SIGNAL INTEGRITY

#### BY HOWARD JOHNSON, PhD

#### In-between spaces

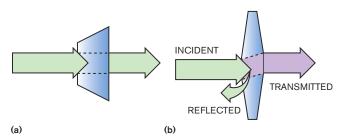

measured the inductance of four loops of wire. Each loop comprises the same length of insulated #10 AWG solid-copper wire (Figure 1). During testing, I probe the wires at their endpoints (bottom of figure), holding the wires vertically above the tester and well away from all other metal objects.

The leftmost loop, the round one, has a diameter of 10 in. It gives the largest inductance at 730 nH. Moving to the right, the inductance drops

in each case until you reach the final loop, the twisted wire, at 190 nH.

I mention this simple experiment because I have all too often heard engineers say: "My via has an induc-

Figure 1 Each loop of wire is the same length, yet they each have inductances, from left to right, of 730, 530, 330, and 190 nH.

Figure 2 Magnetic fields from the outgoing current (red) nearly cancel the equal-but-opposite magnetic fields from the returning signal current.

tance of 1 nH," or "My bypass capacitor has an inductance of 500 pH." Those statements assume that you can ascribe discrete inductances to individual portions of a signal path.

That assumption is a good one when dealing with macroscopic components. According to Kirchhoff's laws for circuit analysis, the total inductance of two inductors in series should equal the sum of their independent inductances.

The correctness of Kirchhoff's analysis hinges upon a crucial precondition, namely that no significant electromagnetic fields inhabit the spaces between conductors. High-speed digital currents infuse the spaces between conductors with massive, fast-changing electromagnetic fields. These digital circuits do not meet Kirchhoff's precondition; therefore, Kirchhoff's laws are invalid in the high-speed domain.

In high-speed electronics, you must supplement Kirchhoff's laws with parasitic capacitance, due to electric fields, and parasitic inductance, due to magnetic fields.

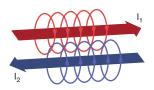

Figure 2 illustrates the pattern of magnetic fields surrounding two wires. The wires carry equal and opposite currents, much like the hairpin structures in Figure 1. Imagine current I<sub>1</sub>

going out on one wire, changing direction at a hairpin turn, and returning as I, on the other wire.

If you observe from a remote distance, the magnetic fields that  $I_1$  generates nearly cancel the equal-but-opposite magnetic fields that  $I_2$  generates. The closer you bring the wires, the better the cancellation, and the smaller the overall magnetic-field energy.

Inductance L represents nothing more and nothing less than the total magnetic-field energy, E, surrounding a current-carrying circuit. The precise relation between inductance and field energy is:

$$E = \frac{1}{2}LI^2.$$

If the spacing between wires affects the stored magnetic energy, then the spacing affects the circuit inductance, as well.

This interaction between magnetic fields explains why you cannot ascribe inductance to one part of a distributed circuit without also specifying the shape and location of the complete signal-current path. It might increase or decrease the inductance. All parts of the path influence the inductance.

For example, the inductance of a via depends on the location of nearby interplane connections. The inductance of a bypass capacitor depends on its proximity to the reference planes.

Inductance is not a property of an individual component. In distributed circuits, inductance is a property of the spaces between conductors.**EDN**

# H Go to www.edn.com/070524hj and click on Feedback Loop to post a comment on this column.

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com or e-mail him at howie03@sigcon.com.

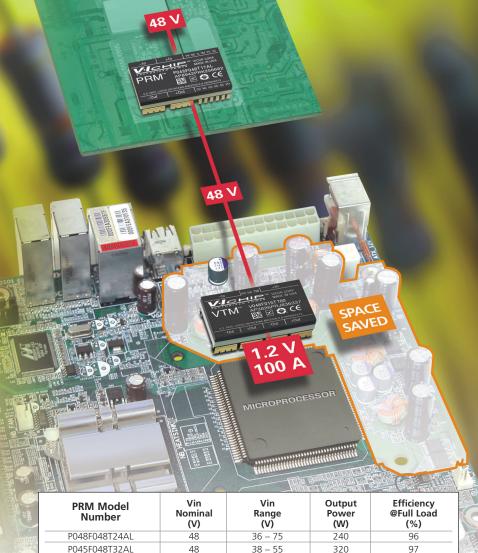

# Half the Size, Half the Loss All the Power